1. DDL(数字延迟线)测试简介

1.1 DDL的基本概念

数字延迟线(DDL)是一个可调的延迟线,其基本作用是增加信号的延迟。DDL常被用于调整时序,使得信号的传输符合系统要求。每个DDL通常充当一个简单的缓冲器(buffer),但可以通过改变延迟值来改变信号到达目的地的时间。

1.2 测试时的问题

在进行逻辑扫描测试时,输入信号会通过DDL传输,并通过输出端传递到下一级电路,验证是否传递了正确的逻辑值(0或1)。然而,逻辑扫描并不能直接测量每个DDL设置的延迟,也不能确认这些延迟组合是否会形成特定的时序特性。因此,DDL的延迟特性不能仅仅通过逻辑扫描来准确评估。

1.3 DDL的类型

1.3.1 LCDL

- 定义:LCDL是长延迟线,具有较大的最大延迟值。它通常用于需要较大时序调整的场景。例如,LCDL可用于调整数据总线(如DQ、DQS等)上的偏移。

- 应用:通常用于调整数据传输的时序,特别是大范围的时序偏移(例如,数据/时钟的同步)。

1.3.2 BDL

- 定义:BDL是短延迟线(相较于LCDL),具有较小的最大延迟值。它通常用于较小范围的时序调整。

- 应用:例如,在DATX8和DATX4X2模块中,BDL主要用于写入和读取比特的去偏移。

1.3.3 NDL

- 定义:NDL是固定延迟线,它的延迟是一个固定值,通常用于与LCDL的零延迟对齐。

- 应用:NDL通常用于某些特定的时序要求,以保证延迟线之间的一致性。

1.4 DDL的可观察性

1.4.1 可观察DDL的情况

并不是所有的DDL都会影响主输出引脚(如DQ、DQS等),有些DDL只影响内部信号节点。对于某些DDL,可以通过测试来观察其延迟的效果。特别是在影响写入比特去偏移的DDL时,通过编程DDL的延迟值寄存器,可以在输出引脚(如DQ、DQS、DM)上观察到信号的时序变化。

1.4.2 直接访问和测试的局限性

尽管一些DDL是可观察的,但并非所有DDL都直接影响主输出引脚。有些DDL只在内部起作用,因此无法通过主引脚直接测试它们。此外,DDL的最小延迟步长通常非常小,这使得常规的自动测试设备(ATE)难以精确测量这些微小的变化。通常,测试时只能在较大的步长范围内进行测量,因此这并不是一个完美的解决方案。

1.5 DDL环振荡器测试模式

1.5.1 环振荡器的基本原理

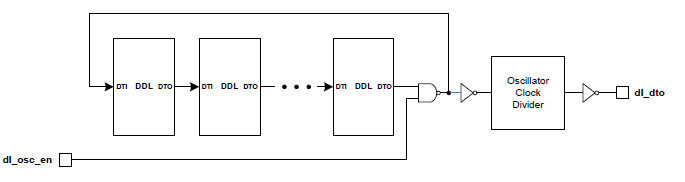

为了能够全面测试DDL,DDR4设计了DDL环振荡器模式。在此模式下,所有的NDL、BDL和LCDL都会被连接成一个环形振荡器。这一环形振荡器是由多个延迟线组成的,通过将一个DDL的数字测试输出(DTO)连接到下一个DDL的数字测试输入(DTI),形成一个闭环。

1.5.2 振荡器的具体连接方式

- 连接方式:环振荡器的结构是将DDL连接成一个环,其中每个延迟线的DTO连接到下一个DDL的DTI,最后一个DDL的DTO通过NAND门连接回第一个DDL的DTI,完成闭环。

- 环路的控制:这个环振荡器的输出信号会通过一个可编程的分频器进行频率降低,以便在控制时钟域(如PUB时钟)中进行处理。

1.5.3 独立测试

每个PHY模块(如DATX8、DATX4X2、AC、ACX48)都具有独立的环振荡器,可以并行测试整个接口。这使得在测试过程中可以同时监测多个DDL的延迟行为,减少测试时间。

1.6 测试DDL的特性

1.6.1 延迟线的特性测试

通过调整DDL的选择输入,可以测试每个DDL的多个特性,包括:

- 存在性测试:确认每个DDL是否正常工作。

- 线性度测试:测试DDL延迟的变化是否随着输入的调整而线性变化。

- 延迟范围测试:确认每个DDL的延迟范围是否满足时序要求。

1.6.2 测量延迟变化

在测试过程中,可以通过调整DDL的选择输入,观察环振荡器输出的周期变化,进而了解DDL的延迟特性。为了提高测量精度,输出信号会通过一个可编程分频器降低频率,以便在较低速时钟下处理这些信号。

1.7 测量方法

1.7.1 分频器和测试分辨率

通过环振荡器的输出,分频器将振荡器的频率降低。这个分频比率可以根据需要进行设置,通常范围从1到65536。选择合适的分频比率可以在测试时调整分辨率和测试时间。

- 分频比率的选择:通过调整分频比率,可以在不同的时间精度和测试分辨率之间进行平衡。例如,如果需要更高的测量精度,可以选择较大的分频比率,但这样可能需要更长的测试时间。

1.7.2 自动周期测量

在测试过程中,PUB(控制单元)中的逻辑可以自动测量环振荡器输出信号的周期,并将结果存储在寄存器中。这个周期值相对于PUB的控制时钟(ctl_clk)来说,是一种相对的周期测量。

2. DDL结构

2.1 DDL的设计结构

数字延迟线(DDL)是由一系列粗延迟单元(coarse delay elements)和一个精细延迟单元(fine delay element)组成的。其设计目的是通过控制延迟元素的数量,调节信号的延迟。

- 粗延迟单元(Coarse Delay Element):这部分用于提供较大的延迟变化,它通常由多个相同类型的单元组成。对于不同类型的DDL(例如BDL和LCDL),粗延迟单元的数量会有所不同。具体来说,BDL包含4个粗延迟单元,而LCDL包含32个粗延迟单元。

- 精细延迟单元(Fine Delay Element):精细延迟单元用于提供非常小的延迟变化,它比粗延迟单元的调整更为细致。BDL和LCDL使用相同类型的精细延迟单元,精细延迟单元的调节步长为16个细节步骤。即,通过精细调节,可以实现非常精确的延迟控制。

2.2 DDL的延迟设置

在设置DDL的延迟时,首先会选择一个合适的粗延迟单元数量。粗延迟单元的数量决定了DDL的基本延迟范围。如果需要更精细的调整,可以启用精细延迟单元。精细延迟单元提供更细粒度的调节,以便在需要时精确地调整信号的延迟。

- BDL:BDL包含16步精细延迟和4步粗延迟。这意味着BDL能够提供相对较小的延迟变化(精细调整)以及较大的延迟步长(粗调整)。

- LCDL:LCDL包含16步精细延迟和32步粗延迟。相比BDL,LCDL可以提供更大的延迟范围,因为它有更多的粗延迟步骤。

3. DDL测试观察

3.1 测试方法概述

测试DDL的效果主要有两种方式。它们都利用了环振荡器输出信号(即环振荡器生成的时钟信号),这个信号经过一定的处理后送到PUB(控制单元)进行进一步测试和观测。

3.2 第一种测试方法:由PUB计算频率

在这种测试方法中,环振荡器的输出信号(经过可编程分频器分频)被传送到PUB。PUB使用其内部的控制时钟(ctl_clk)对环振荡器的输出信号进行采样,并通过某种数学运算计算出一个代表环振荡器频率的值。

- 采样过程:由于PUB的控制时钟可能在较慢的速度下运行,因此可以通过设置适当的时钟分频比率(分频器的值)来确保测试的准确性和效率。

- 测试的优点:这种方法通过自动计算频率,可以快速得到环振荡器频率的结果,并且能够并行测试多个PHY模块(如AC、ACX48、DATX8、DATX4X2)。这使得整体测试时间得以缩短。

3.3 第二种测试方法:直接观察分频后的时钟信号

另一种测试方法是将环振荡器输出信号通过分频器后,直接输出到数字测试输出(DTO)。通过这种方式,用户可以直接观察到环振荡器的时钟波形。

- 优点:这种方法适合在设备调试或表征时使用,能够让工程师直接看到时钟信号的波形,帮助调试和理解DDL的延迟行为。

- 局限性:尽管这种方法在调试时有用,但它并不适合作为生产测试的标准方式。在生产测试中,如果每个PHY模块都需要单独观察时钟波形,测试时间会大大增加,因为只能同时测试一个PHY模块。

3.4 比较两种测试方法

- 方法一:PUB计算频率:

- 优点:可以并行测试多个PHY模块,测试时间较短。

- 适用场景:生产测试,能够快速获取频率值。

- 方法二:直接观察信号波形:

- 优点:可以直观地看到信号波形,适用于设备调试和表征。

- 缺点:只能一次测试一个PHY模块,测试效率较低,不适合生产环境。

4. 测试方法

4.1 DDL测试的整体框架

PHY模块与PUB控制单元共同提供DDL环振荡器模式测试功能。通过使用PUB的可编程寄存器控制测试过程,测试方法可以根据需求进行定制。例如,在生产测试中,可能会选择进行采样测试,以减少测试时间,而将详尽测试保留用于样本测试或质量保证(QA)环节。在这种方法中,测试的样本大小或类型可以根据产品的需求进行调整。

4.2 测试方法概述

建议的DDL测试方法包括两个主要步骤:设置测试环境和实际进行测试。具体步骤如下:

步骤1:设置PUB和PHY宏进行DDL测试

在进行DDL测试之前,首先需要设置PUB和PHY宏的相关参数,确保测试环境配置正确。

a. 如果计划观察DDL振荡器测试模式输出到DTO I/O接口,启用DTO I/O并确保其不处于电源关闭状态:

- DSGCR.DTOPDR =

1'b0(不处于电源关闭) - DSGCR.DTOOE =

1'b1(启用DTO输出)

b. 可选择将PLL和I/O设备置于电源关闭模式,通过写入其相应的电源控制寄存器来实现。

c. 禁用VT计算并禁用VT漂移补偿,通过设置VT漂移限制为0:

- PGCR6.INHVT =

1'b1(禁止VT计算) - PGCR6.DLDLMT =

9'h00(将VT漂移限制设置为0)

d. 重置PHY宏,但不重置PUB逻辑,并禁用地址/命令通道MDL校准:

- PGCR1.PHYHRST =

1'b0(禁用PHY重置) - PGCR1.MDLEN =

1'b0(禁用MDL校准)

注意: 在仿真中,PHY宏需要重置以防止读取数据被错误地反馈到DFI控制器中,但在正常测试中DFI控制器不活跃,因此FIFO是否处于重置状态不影响测试。

e. 禁用字节通道MDL校准和字节通道的占空比校正:

- DXCCR.MDLEN =

1'b0(禁用字节通道MDL校准) - DXCCR.DXDCCBYP =

1'b1(跳过字节通道占空比校正) - PGCR4.ACDCCBYP =

1'b1(跳过地址/命令占空比校正)

f. 解除PHY宏的重置(该重置不会自动清除):

- PGCR1.PHYHRST =

1'b1(解除PHY重置)

g. 启用延迟线振荡器测试模式:

- PGCR0.DLTMODE =

1'b1(启用DDL测试模式)

h. 等待至少100ns。

i. 将PHY模块中的所有DDL设置为最小延迟(0x0)。

步骤2:测试DDL

在设置好测试环境后,开始测试每个DDL。测试过程按照以下步骤进行:

a. 选择一个DDL进行测试。

b. 启用DDL振荡模式并设置所需的振荡器分频比:

- PGCR0.OSCEN =

1'b1(启用振荡器) - PGCR0.OSCDIV = 所需的振荡器分频比

- PGCR0.DTOSEL = 选择输出DTO的PHY实例

如果选择的是LCDL(大范围延迟线),确保只选择该LCDL并通过设置以下寄存器选择正确的LCDL:

- PGCR0.OSCWDL, PGCR0.OSCWDDL, PGCR0.OSCACDL:根据LCDL的选择设置为正确值。

c. 等待一个未确定的时间(TBD)。

d. 触发DDL测试输出周期测量:

- PGCR0.DLTST =

1'b1(触发DDL测试)

e. 等待DDL测试输出周期测量完成,通过轮询PGSR1.DLTDONE来确认:

- 对于AC/ACX48模块,检查 PGSR1.DLTDONE =

1'b1。 - 对于DATX8/DATX4X2模块,检查 DXnGSR1.DLTDONE =

1'b1。

f. 读取测量的周期值:

- 对于AC/ACX48模块,读取 PGSR1.DLTCODE。

- 对于DATX8/DATX4X2模块,读取 DXnGSR1.DLTCODE。

g. 禁用DDL振荡和测量功能:

- PGCR0.OSCEN =

1'b0(禁用振荡器) - PGCR0.DLTST =

1'b0(禁用DDL测试)

h. 增加精细延迟元素一步并重复步骤2b到2h。

i. 一旦完成所有精细步设置,将精细延迟设置回最小值(0x0),并增加粗延迟元素一步。重复步骤2b到2i,但跳过步骤2h(即保持精细延迟代码最小值)。

j. 完成所有粗延迟步骤后,你将获得每个精细和粗延迟步骤的测试结果记录。

k. 将DDL的延迟代码设置回最小值,并切换到PHY模块中的下一个DDL。重复测试直到所有DDL都完成。

通过标准

每个DDL的测试通过标准如下:

- 每个增量精细步的值必须大于上一个步的值。

- 第一个粗步的值必须等于或大于精细元素的最大值。

- 每个增量粗步的值必须大于上一个步的值。

为了减少测试时间,因为粗延迟的最小步长大于精细延迟步长,可以在测试粗延迟时使用较小的输出时钟分频比。

并行测试:

- AC/ACX48和每个DATX8/DATX4X2模块可以并行测试,因此需要为每个模块配置适当的寄存器并同时读取测试结果。

- AC/ACX48与DATX8/DATX4X2的测试有所不同,因为它们使用的BDL和LCDL数量不同。

本文链接: https://talent-tudou.github.io/2024/11/26/DDR/Design For Test-DDL TEST/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!